파이프라이닝 (Pipelining)

프로세서 아키텍처에서의 파이프라이닝(Pipelining)은 CPU의 성능을 향상시키는 중요한 기술이다.

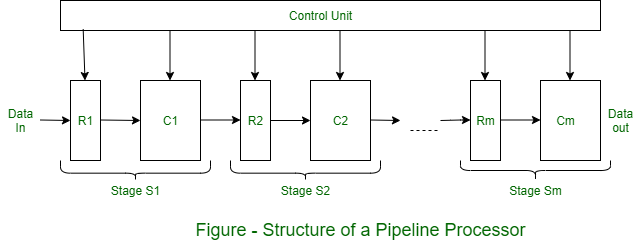

파이프라이닝은 여러 명령어의 실행 단계를 중첩시켜 전체적인 처리량을 향상시키는 기술로, 여러 단계를 동시에 처리함으로써 효율성을 높인다.

현대 프로세서 설계에서 필수적인 기술이며, 대부분의 현대 CPU는 최소 2단계에서 최대 30-40단계의 파이프라인을 사용한다.

이 기술을 통해 프로세서의 전체적인 성능을 크게 향상시킬 수 있지만, 효과적인 구현을 위해서는 복잡한 설계 고려사항들을 신중히 관리해야 한다.

파이프라이닝의 작동 원리

파이프라이닝은 명령어 실행 과정을 여러 단계로 나누어 처리한다.

일반적인 파이프라인 단계는 다음과 같다:

- 명령어 인출 (Instruction Fetch, IF)

- 명령어 해독 (Instruction Decode, ID)

- 실행 (Execution, EX)

- 메모리 접근 (Memory Access, MEM)

- 레지스터 쓰기 (Write Back, WB)

각 단계는 동시에 다른 명령어를 처리할 수 있어, 전체적인 처리 속도가 향상된다.

파이프라이닝의 장점

- 처리량 증가: 여러 명령어를 동시에 처리하여 전체적인 처리량이 증가한다.

- CPU 활용도 향상: 파이프라이닝을 통해 CPU의 각 부분이 지속적으로 활용되어 유휴 시간이 줄어든다.

- 클록 주파수 향상: 파이프라이닝을 사용하면 CPU의 산술 논리 장치를 더 빠르게 설계할 수 있다.

- 반복적 작업에서의 성능 향상: 특히 반복적인 작업에서 파이프라이닝의 효과가 두드러진다.

파이프라이닝의 단점

- 설계 복잡성: 파이프라인 프로세서의 설계가 더 복잡하고 제조 비용이 높다.

- 파이프라인 해저드: 데이터 의존성, 제어 흐름 변경, 자원 충돌 등으로 인한 파이프라인 해저드가 발생할 수 있다.

- 분기 예측의 어려움: 분기 명령어로 인해 파이프라인이 비워져야 할 때 성능 저하가 발생할 수 있다.

- 레이턴시 증가: 파이프라인 단계 사이에 플립플롭을 삽입함으로써 개별 명령어의 레이턴시가 증가할 수 있다.

파이프라이닝의 구현

파이프라이닝을 구현할 때는 다음과 같은 요소들을 고려해야 한다:

- 파이프라인 깊이: 파이프라인 단계의 수를 결정한다. 더 많은 단계는 더 높은 처리량을 제공할 수 있지만, 해저드 관리가 더 복잡해진다.

- 해저드 관리: 데이터 의존성, 제어 흐름 변경, 자원 충돌 등의 해저드를 효과적으로 관리해야 한다.

- 분기 예측: 분기 명령어로 인한 성능 저하를 최소화하기 위해 효과적인 분기 예측 기법을 사용한다.

- 클록 주파수 최적화: 파이프라인 단계를 균형있게 설계하여 최적의 클록 주파수를 달성한다.