System Bus

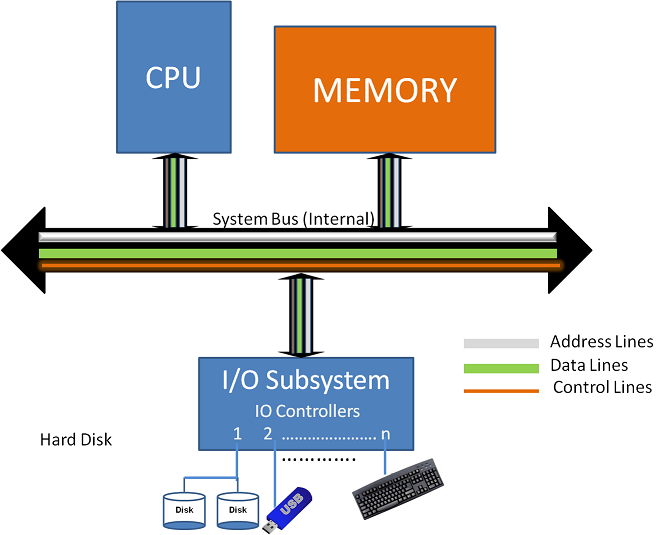

System Bus는 컴퓨터 아키텍처에서 주요 구성 요소들을 연결하는 중요한 통신 경로로, 컴퓨터의 혈관과 같은 역할을 한다. CPU, 메모리, 입출력 장치 등 컴퓨터의 주요 구성 요소들 사이에서 데이터와 신호를 전달한다.

시스템 버스의 주요 구성 요소

시스템 버스는 세 가지 주요 버스로 구성된다:

데이터 버스 (Data Bus):

- 양방향 버스로, 시스템 구성 요소들 사이에서 실제 데이터를 전송한다.

- 예를 들어, CPU가 메모리에서 데이터를 읽거나 쓸 때 사용된다.

- 버스의 폭(width)은 한 번에 전송할 수 있는 데이터의 양을 결정한다.

주소 버스 (Address Bus):

- 단방향 버스로, 메모리나 I/O 장치의 주소를 지정한다.

- CPU가 접근하고자 하는 메모리 위치를 지정할 때 사용된다.

- 버스의 폭은 시스템이 접근할 수 있는 메모리의 최대 크기를 결정한다.

제어 버스 (Control Bus):

- 양방향 버스로, 시스템의 동작을 제어하는 신호를 전달한다.

- 읽기/쓰기 신호, 인터럽트 신호, 클록 신호 등을 전달한다.

- 데이터 전송의 타이밍과 방향을 조정한다.

시스템 버스의 동작 방식

시스템 버스의 기본적인 동작 과정은 다음과 같다:

- 메모리 읽기 연산:

- CPU가 주소 버스에 메모리 주소 전송

- 제어 버스를 통해 읽기 신호 전송

- 메모리가 데이터 버스를 통해 데이터 전송

- 메모리 쓰기 연산:

- CPU가 주소 버스에 메모리 주소 전송

- 데이터 버스에 쓸 데이터 전송

- 제어 버스를 통해 쓰기 신호 전송

기능

- 데이터 전송: 구성 요소 간 정보 교환

- 주소 지정: 메모리 위치나 I/O 장치 식별

- 제어 신호 전달: 읽기/쓰기 작업 등의 동작 제어

시스템 버스의 특성

동기화 (Synchronization):

- 버스 클록이 모든 데이터 전송을 동기화한다.

- 클록 속도는 버스의 성능을 결정하는 주요 요소이다.

중재 (Arbitration):

- 여러 장치가 동시에 버스를 사용하려 할 때의 충돌을 방지한다.

- 우선순위에 따라 버스 사용 권한을 할당한다.

멀티플렉싱 (Multiplexing):

- 한정된 버스 라인을 효율적으로 사용하기 위해 시분할 방식을 사용한다.

- 주소와 데이터를 같은 라인으로 전송할 수 있다.

시스템 버스의 성능 향상 기법

버스 폭 확장:

- 더 넓은 데이터 버스를 사용하여 한 번에 더 많은 데이터를 전송한다.

- 32비트에서 64비트, 128비트로 확장하는 방식이다.

계층적 버스 구조:

- 여러 종류의 버스를 계층적으로 구성하여 성능을 최적화한다.

- 예: CPU 버스, 메모리 버스, I/O 버스 등의 분리

버스 파이프라이닝:

- 여러 버스 작업을 중첩하여 처리함으로써 성능을 향상시킨다.

- 한 작업이 완료되기 전에 다음 작업을 시작할 수 있다.

성능 영향

- 버스 속도: 데이터 전송 속도에 직접적 영향

- 버스 폭: 한 번에 전송할 수 있는 데이터 양 결정